2024 IEEE International Symposium on Integrated Circuits and Systems (ISICAS 2024)

## PRESENTATION TITLE Accelerated Image Processing Through IMPLY-Based NoCarry Approximated Adders Presenter Name

Nima TaheriNejad

#### SYSTEMS & CIRCUITS FOR A SUSTAINABLE SOCIETY

#### OUTLINE

Introduction & Motivation

**Problem Statement**

Methodology

Results

#### **MOTIVATION**

[S]**C?**S 2024 delhi, india

© Copyright

#### www.isicas2024.org

## INTRODUCTION

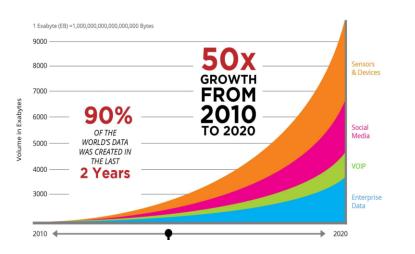

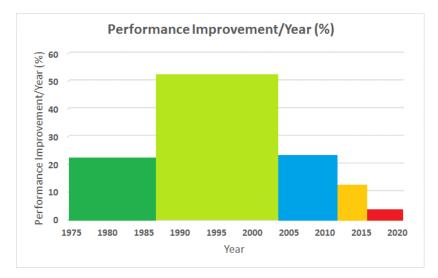

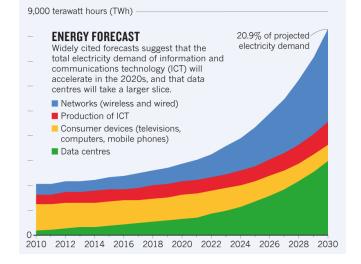

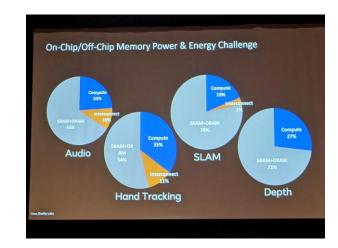

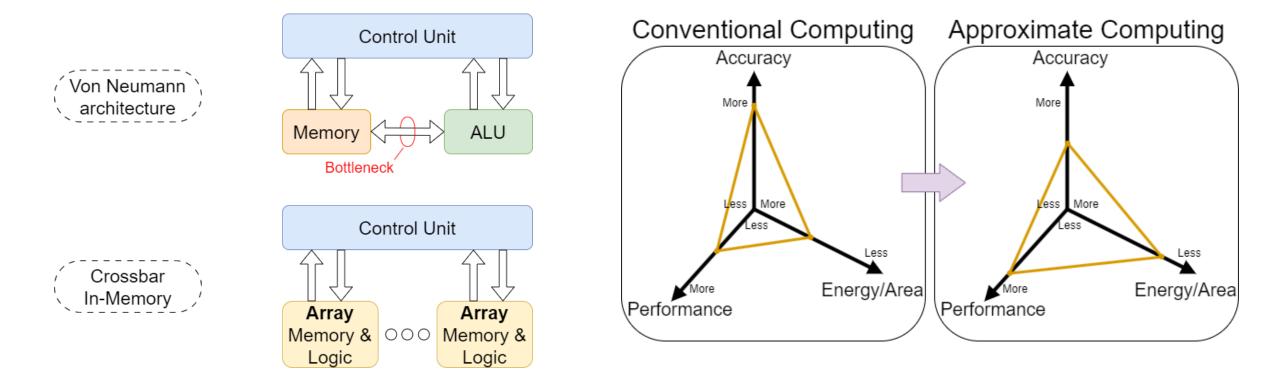

- Von Neumann Bottleneck => Memristor & In-Memory Computing [1]

- Power Wall Problem => Approximate Computing

#### www.isicas2024.org

## **PROBLEM STATEMENT**

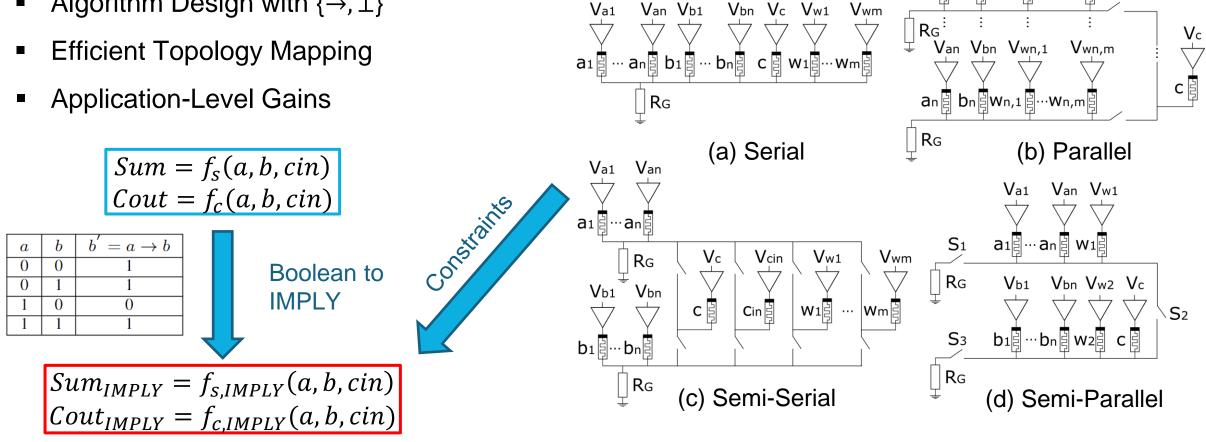

- Approximate + In-Memory Computing

- Algorithm Design with  $\{\rightarrow, \bot\}$

Memristor

Voltage Source

Resistor

Vw1,m

Va1 Vb1 Vw1,1

a1 🛓 b1 🛓 W1,1 🛓 … W1,m 🛓

#### **METHODOLOGY**

**Disregard Carry Propagation** [2]

No Carry +

Cout

© Copyright

Sum

- **Functional Representation**

- Evaluation

Inputs

b

-1

а

С

**Equivalent IMPLY Function**

Exact

Cout

Sum

No Carry

Cout

Sum

| A <sub>n-1:n-k</sub> B <sub>n-1:n-k</sub><br>k-bit<br>Precise Adder<br>S <sub>n-1:n-k</sub> |                                                                                           |                                               |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|

| Error Evaluation                                                                            | $Sum_i = a_i + b_i$ $Cout_i = a_ib_i$                                                     | $Sum_i = a_i + b_i$ $Cout_i = 0$              |

|                                                                                             |                                                                                           |                                               |

|                                                                                             | NoCarry+                                                                                  | NoCarry                                       |

|                                                                                             | $Sum_{i} = \overline{a_{i}} \to b_{i}$ $Cout_{i} = \overline{a_{i}} \to \overline{b_{i}}$ | $Sum_i = \overline{a_i} \to b_i$ $Cout_i = 0$ |

ΔιζΔιζΔις

75 🧟 🔶 IEEE

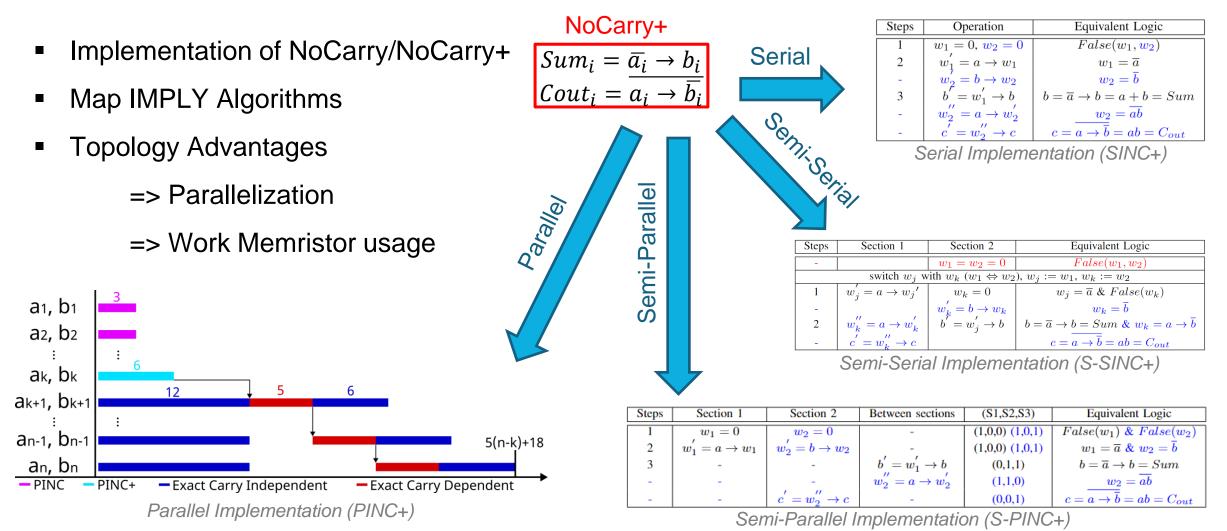

#### **METHODOLOGY – MAPPING**

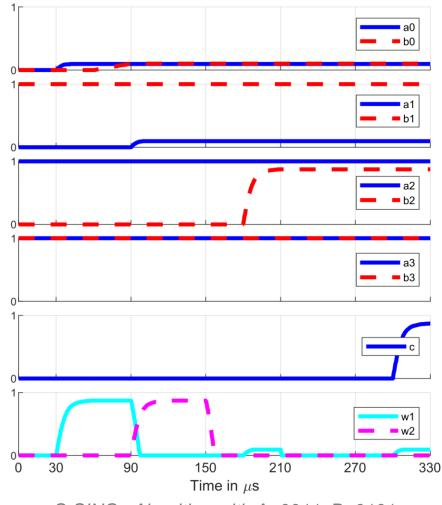

#### **METHODOLOGY – SIMULATION**

- 8 Approximated Algorithms (4 Topologies)

- VTEAM Model [3] in SPICE

- Fitted to measurements

- ATOMIC Pipeline

- => Stateful Logic Validation

- => Automated SPICE Simulations

- => Energy Calculations

- => Deviation Experiments

- Correct Behavior with ±30% Deviation

Get ATOMIC access here: https://github.com/fabianseiler/ATOMIC

S-SINC+ Algorithm with A=0011, B=0101

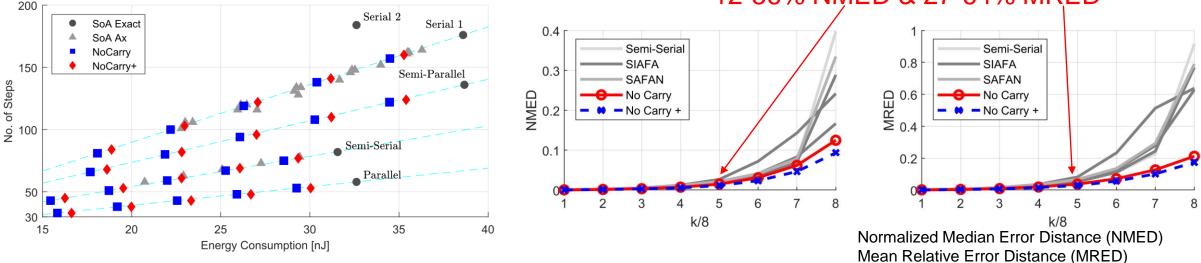

#### RESULTS

- Comparison to Exact Adder

- => 6-54% Faster

- => 7-54% less Energy

- => Up to **12%** fewer Memristors

- => Up to **63**% fewer Switches

- Comparison to Approximated Adder (5/8)

- => 17-30% Faster

- => 17-33% less Energy

- => Improved Error Metrics

#### 12-56% NMED & 27-64% MRED

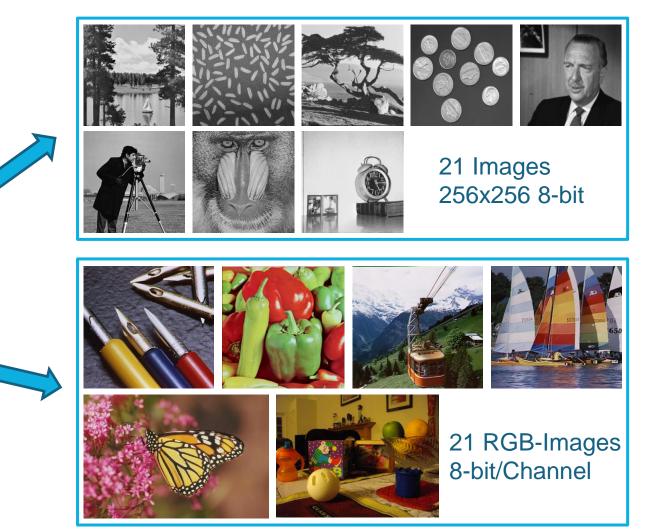

### **IMAGE PROCESSING – OVERVIEW**

- Error-resilient Application

- Quality Metrics

=> PSNR

=> SSIM

Proposed Datasets

=> Image Addition

=> Grayscale Filter

Highway Dataset [4]

=> Background Subtraction

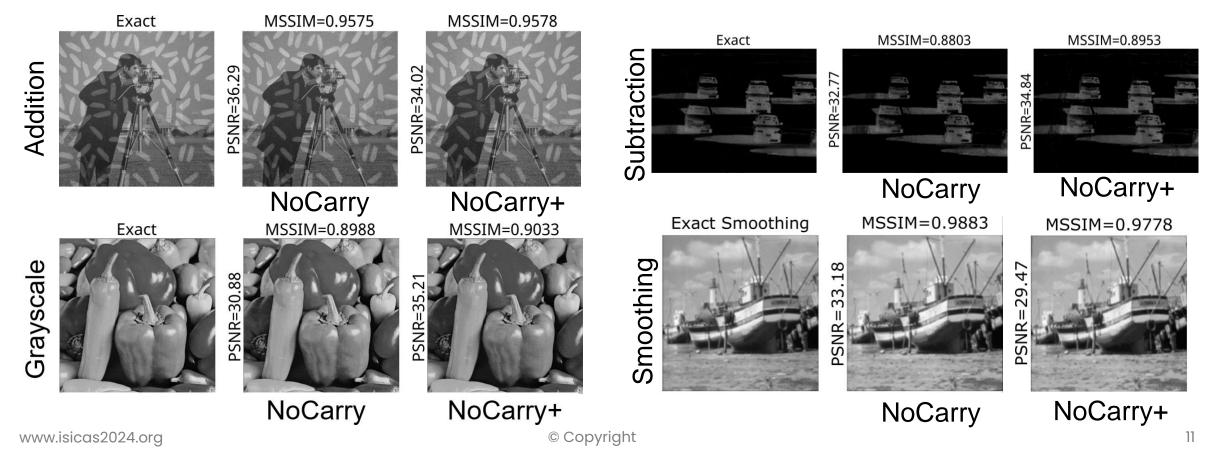

#### **IMAGE PROCESSING – RESULTS**

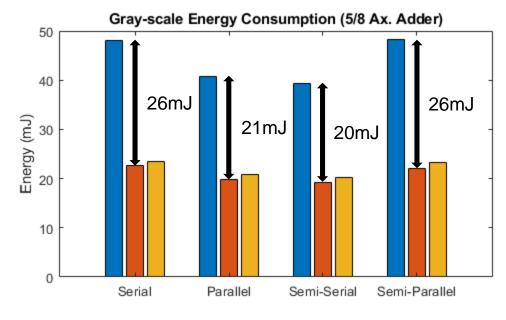

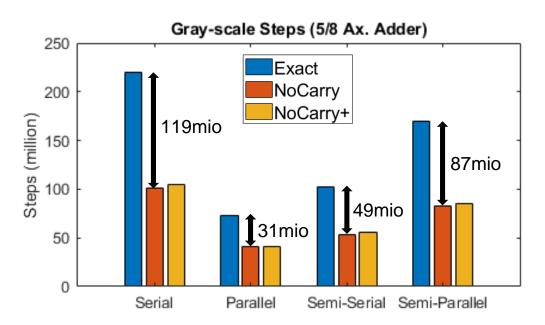

- Image Addition & Grayscale Filter (5/8 Ax Adder)

- Image Subtraction (5/8 Ax Adder) & Gaussian Smoothing (86% Ax)

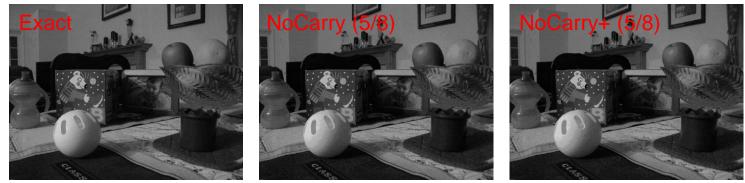

#### **IMAGE PROCESSING – GAINS**

- 684x912 RGB-Image

- 20-26 mJ Energy

- 31-119 million Steps

#### 13

#### CONCLUSION

- 8 Approximated Implementations

- In 4 Topologies => Design Space Exploration

- Saved 6-54% Energy & 7-54% Steps

- Proposed 2 Image Processing Datasets

- Improved Image Quality & More Efficient than SoA

© Copyright

75 🧟 🔶 IEEE

- [1] N. TaheriNejad. In-memory computing: Global energy consumption, carbon footprint, technology, and products status quo. pp. 1–6, 2024

- [2] H. R. Mahdiani et al. Bio-inspired imprecise computational blocksfor efficient vlsi implementation of softcomputing applications. IEEETransactions on Circuits and Systems I: Regular Papers, 57(4):850– 862,2010

- [3] S. Kvatinsky et al. Vteam: A general model for voltage-controlledmemristors. IEEE Transactions on Circuits and Systems II: ExpressBriefs, 62(8):786–790, 2015.

- [4] A. Prati et al. Detecting moving shadows: algorithms and evalua-tion. IEEE Transactions on Pattern Analysis and Machine Intelligence, 25(7):918–923, 2003

- Presented Datasets: github.com/fabianseiler/Ax-Image-Processing

- **ATOMIC Tool:** github.com/fabianseiler/ATOMIC

2024 IEEE International Symposium on Integrated Circuits and Systems (ISICAS 2024)

# Questions & Answers

#### SYSTEMS & CIRCUITS FOR A SUSTAINABLE SOCIETY

www.isicas2024.org

© Copyright

# **THANK YOU**